如果按照实验书上一步步做到也不是很难,可是老师要求要在数码管上显示,这对我来说就有些麻烦了,向来讨厌数码管显示。

硬着头皮做了近10个小时了,总算是仿真正确了,至于硬件测试,希望不要在有什么乱子。

序列检测器是时序数字电路中非常常见的设计之一。它的主要功能是:将一个指定的序列从数字码流中识别出来。接下来就以设计“01101”这个序列的检测器为例,说明Verilog HDL语言的具体应用。设X为数字码流输入,Z为检出标记输出,高电平表示“发现指定序列”,低电平表示“没有发现指定的序列”。设输入的码流为“001101101111011111...”,在时钟2~6中,码流X里出现指定序列“01101”,对应输出Z在第6个时钟变为高电平“1”,表示发现指定"01101”,Z输出“1”。同理在第9个时钟对应输出Z也为“1”。根据这个逻辑功能描述,我们可以分析得出状态转换图。

设计思路:

首先用状态图输入法生成序列检测器。

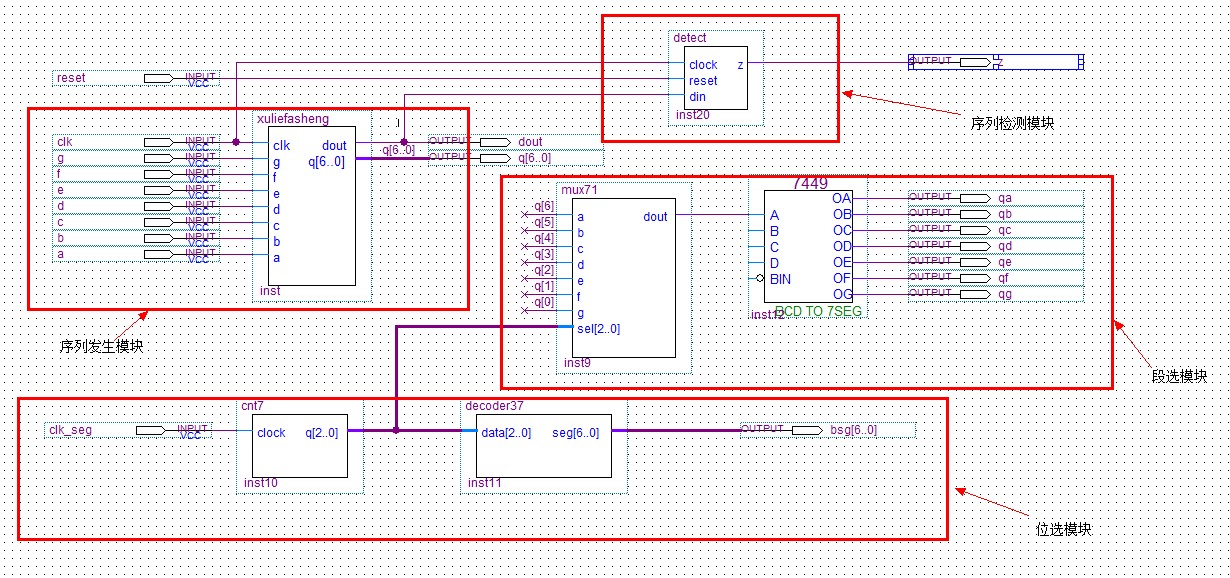

为了便于硬件测试,首先设计一个能够依次产生1110010序列的序列发生器,该序列发生器应该具有预置序列输入端,时钟输入端,串行输出端,并行输出端。

位选电路:用7个数码管,从右至左扫描。模拟数据左移。需要用到模7计数器,3线7线译码器。

段选电路:序列发生器并行输出端经过7选1多路选择器,接7段译码器7449。在数码管上显示输入序列。

设计过程:

1、首先用状态图输入法完成序列检测器的设计,检测序列为:1110010

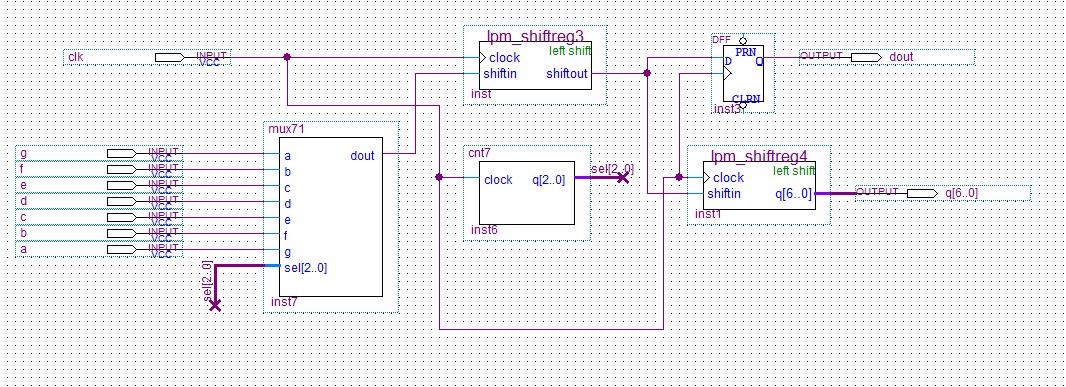

2、序列发生模块设计

用lpm定制一个左移串入串出移位寄存器和一个左移串入并出移位寄存器。

用7选1多路选择器mux71产生特定序列,输入lpm_shiftreg3的串入端。mux71由lpm_shiftreg3的时钟驱动。

为了产生串出的数据以便接到序列检测器和并出的数据以便数码管显示,在加一个串入并出寄存器lpm_shiftreg4,仿真测试时发现lpm_shiftreg4会慢一个时钟周期,所以在串出端dout前加一个D触发器,同步串出和并出的时钟。

然后生成VHDL文件和符号文件,复制.bsf和.vhd文件在新工程中使用。

3、顶层设计

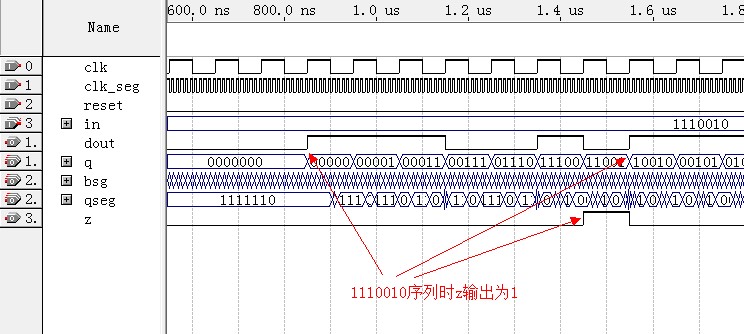

仿真测试:

计数序列为1110010时z输出为1,检测结果正确

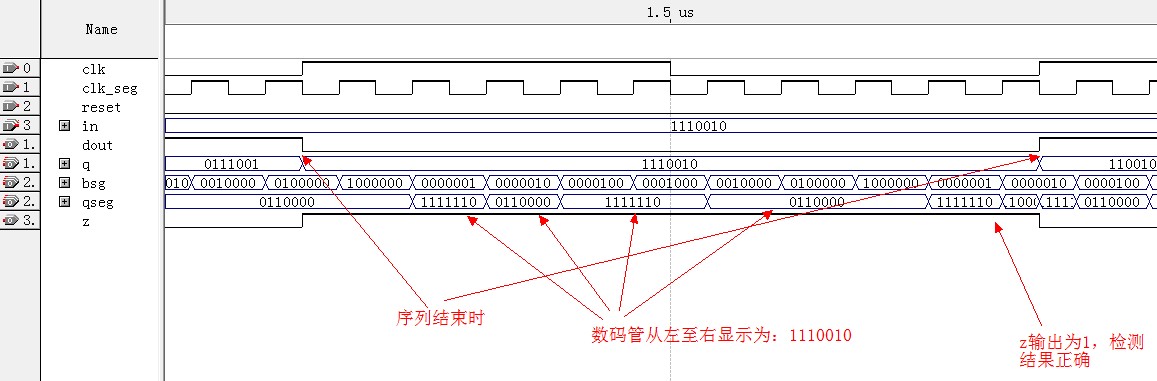

局部大图:

数码管显示为1110010,显示结果正确

附:相关底层设计

模7计数器cnt7,移位寄存器由lpm定制

7选1多路选择器mux71

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

library ieee; use ieee.std_logic_1164.all; entity mux71 is port ( a,b,c,d,e,f,g:in std_logic; sel:in std_logic_vector(2 downto 0); dout:out std_logic); end ; architecture mux71_arch of mux71 is begin dout<= g when sel="000" else f when sel="001" else e when sel="010" else d when sel="011" else c when sel="100" else b when sel="101" else a; end mux71_arch; |

3路7路译码器

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 |

library ieee; use ieee.std_logic_1164.all; entity decoder37 is port( data:in std_logic_vector(2 downto 0); seg:out std_logic_vector(6 downto 0)); end decoder37; architecture rtl of decoder37 is begin process(data) begin case data is when "000" =>seg<="0000001"; when "001" =>seg<="0000010"; when "010" =>seg<="0000100"; when "011" =>seg<="0001000"; when "100" =>seg<="0010000"; when "101" =>seg<="0100000"; when "110" =>seg<="1000000"; when others =>null; end case; end process; end rtl; |

Pingback: 数码管显示VHDL设计 | 知行近思