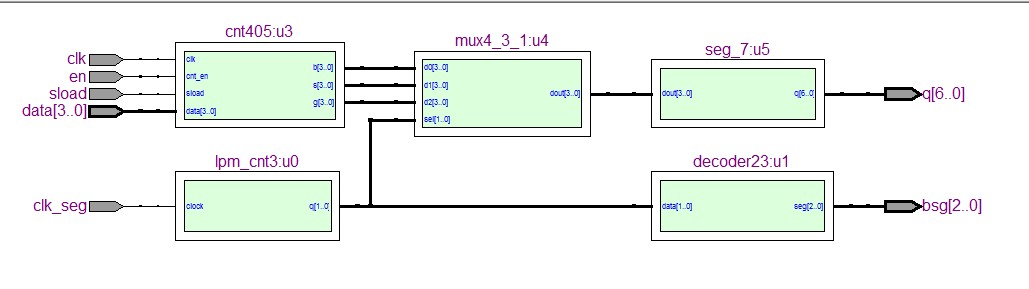

模405计数器加位选和段选之后可以在数码管上直观的显示。

下面是顶层设计,加入相关底层文件即可:

--模405计数器数码管显示顶层设计

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity cntxuehao_7seg is

port(clk_seg,clk,en,sload:in std_logic;

data:in std_logic_vector(3 downto 0);

bsg:out std_logic_vector(2 downto 0);

q:out std_logic_vector(6 downto 0));

end cntxuehao_7seg;

architecture rtl of cntxuehao_7seg is

--模3计数器声明

component lpm_cnt3

port( clock:in std_logic;

q:out std_logic_vector(1 downto 0));

end component;

--2_3译码器声明

component decoder23

port( data:in std_logic_vector(1 downto 0);

seg:out std_logic_vector(2 downto 0));

end component;

--模405计数器声明

component cnt405

port(clk,cnt_en,sload:in std_logic;

data:in std_logic_vector(3 downto 0);

b:out std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

g:out std_logic_vector(3 downto 0));

end component;

--3选1多路选择器声明

component mux4_3_1

port( d0,d1,d2:in STD_LOGIC_VECTOR(3 downto 0);

sel:in STD_LOGIC_VECTOR(1 downto 0);

dout:out STD_LOGIC_VECTOR(3 downto 0));

end component;

--7段译码器声明

component seg_7

port( dout:in std_logic_vector(3 downto 0);

q:out std_logic_vector(6 downto 0));

end component;

--内部连线

signal sel:std_logic_vector(1 downto 0);

signal bai:std_logic_vector(3 downto 0); --百位

signal shi:std_logic_vector(3 downto 0); --十位

signal ge:std_logic_vector(3 downto 0); --个位

signal sel_out:std_logic_vector(3 downto 0); --3选1多路选择器选出数据

--元件例化,端口映射

begin

u0:lpm_cnt3 port map(clk_seg,sel);

u1:decoder23 port map(sel,bsg);

u3:cnt405 port map(clk,en,sload,data,bai,shi,ge);

u4:mux4_3_1 port map(bai,shi,ge,sel,sel_out);

u5:seg_7 port map(sel_out,q);

end rtl;

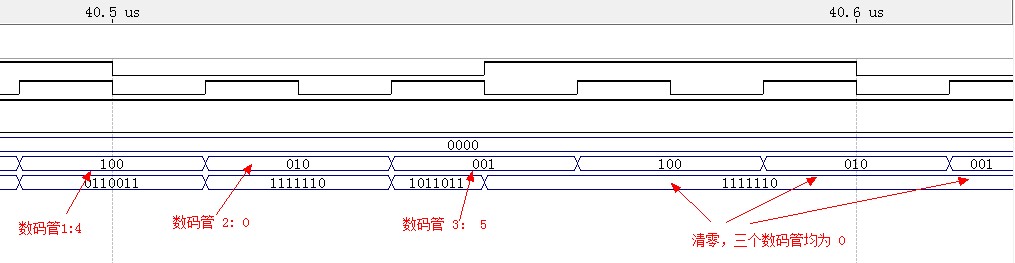

仿真:

发表回复